歡迎來到實佳電子-線路板制造!

?

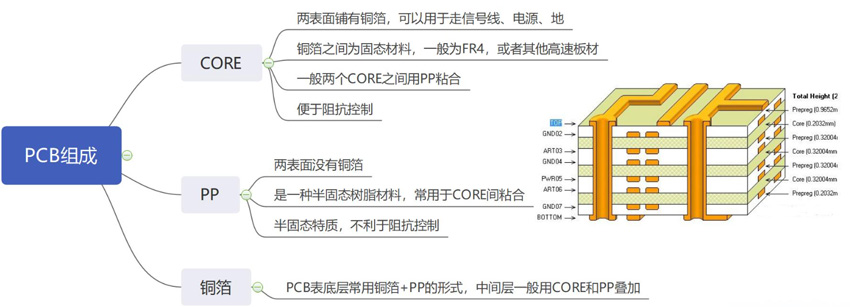

在印制電路板(PCB)設計的廣闊領域中,疊層安排無疑是一個既基礎又至關重要的環節。它不僅關乎電路功能的實現,還直接影響到電磁兼容性(EMC)、信號完整性以及整體系統的性能表現。本文將深入探討疊層安排的原則、技巧及其在實際設計中的應用。

?疊層安排的基本原則?

設計PCB時,首先需要權衡的是成本、功能需求、電磁干擾抑制以及信號完整性等多個方面。布線層和電源/地平面的數量,往往是根據具體的設計要求來確定的。這些要求包括但不限于電路的功能復雜度、噪聲指標、信號的分類(如數字、模擬、高速、低速等)、網線數量(即線條數)以及布局空間的限制等。

?帶狀線與微帶線的應用?

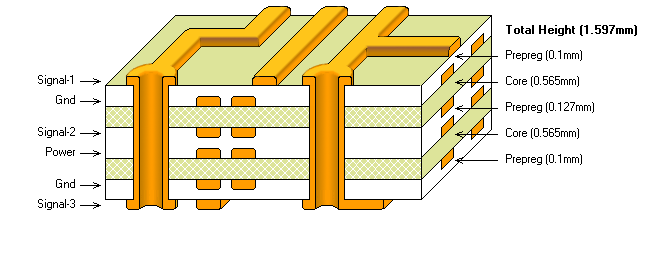

為了抑制PCB中的射頻干擾(RF),并確保信號的完整性,合理采用帶狀線和微帶線結構顯得尤為重要。帶狀線被夾在兩層接地平面之間,可以有效地減少電磁輻射和干擾;而微帶線則位于一層接地平面上方,適用于低速或中等速度的信號傳輸。通過優化這兩種傳輸線的結構,可以顯著降低反射和抖動,從而有效控制RF能量的發射。

?金屬平面的抑制作用?

將金屬平面(如電源平面或接地平面)嵌入PCB中,是抑制共模RF能量的重要手段之一。與依賴金屬機箱或導電塑料盒來封閉RF能量的方法相比,這種方法更為直接且有效。嵌入的金屬平面能夠顯著降低高頻源的分布阻抗,從而更有效地抑制電磁干擾。

?疊層安排的靈活性與適應性?

盡管存在一些通用的疊層安排原則,但每個設計都是獨一無二的。因此,疊層安排必須根據具體的設計要求進行調整和優化。重要的是要確保每個布線層都與一個參考平面(電源或地)相鄰,以提高信號的完整性并降低干擾。然而,對于最外層的微帶線或單層板而言,這一規則可以有所放寬,但應僅限于低速線條,并避免承載高頻或富含RF能量的信號。

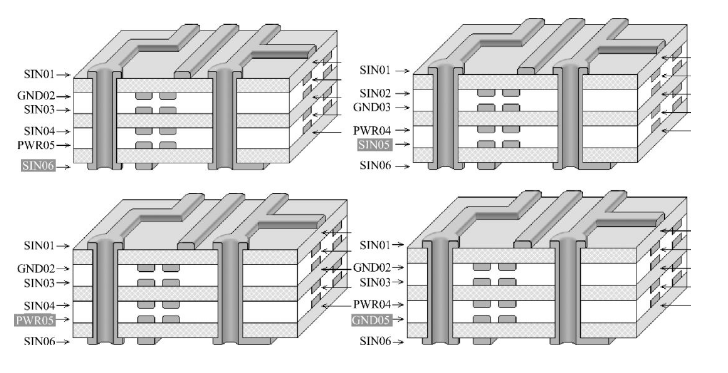

?多層PCB的疊層安排示例?

在多層PCB設計中,可能會出現三層或更多層參考平面的情況。例如,一個電源層與兩個接地層相結合的配置。在這種配置中,與零伏(0V)參考平面相鄰的布線層通常更適合用于高速信號傳輸,因為它們能夠更有效地抑制EMI。這一原則基于PCB上抑制EMI技術的基本概念,即通過合理的疊層安排來降低電磁干擾。

?參考平面的電位固定與噪聲控制?

零電位平板通常通過螺釘固定在機架上,從而將其電位強制固定在地電位。然而,這種固定方式也可能導致接地反沖和板間感應噪聲電壓的問題。為了緩解這些問題,設計師需要仔細考慮參考平面的電位固定方式以及其對整體性能的影響。在某些情況下,可能需要采用額外的接地措施或優化布局來降低噪聲。

?IC大電流與疊層安排的關系?

IC在PCB中的大電流分布與疊層中參考平面的位置密切相關。IC通過管殼與散熱片、屏蔽箱壁等大金屬結構之間的電容耦合,可能會產生顯著的輻射干擾。這種耦合效應會受到疊層安排的影響。因此,在多層板設計中,將接地平面合并為一層(通常位于第二層)可以加強抑制RF能量的作用,因為它能夠減小耦合到機殼上的寄生電容。這一原理在疊層設計時必須予以充分考慮。

綜上所述,電磁兼容的電路板設計之疊層安排是一個復雜而細致的過程。它要求設計師具備深厚的電磁學知識、豐富的實踐經驗以及對新技術和新方法的敏銳洞察力。通過不斷優化疊層安排,可以顯著提升PCB的性能表現并降低電磁干擾的風險。